Objectif :

Additionner deux nombres binaires sans utiliser l'addition et le programmer en  .

.

Un booléen en logique et en programmation est un type de donnée à deux états. Les variables de ce type sont ainsi soit à létat vrai soit à l'état faux (en anglais true et false.

Généralement les conditions sont de type booléen, car elles nécessitent une réponse binaire du type oui ou non.

La plus part des langages utilisent les nombres pour représenter des booléens : par exemple le 0 est faux et toute autre valeur est vrai (la convention n'est pas universelle).

Il est possible d'utiliser un unique bit en mémoire pour stocker une valeur booléenne.

On utilisera cette propriété pour écrire les nombres binaires. Au lieu de les écrire avec des 0 et des 1, on les écrira comme une suite de vrai ou de faux.

On définit sur ces valeurs booléennes trois opérations :

Le NON logique d'un booléen a se définit par :

| a | NON a |

|---|---|

| 0 | 1 |

| 1 | 0 |

Le ET logique entre deux booléens a et b se définit par :

| a | b | a ET b |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Le OU logique entre deux booléens a et b se définit par :

| a | b | a OU b |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Démontrasion des lois de Morgan

| a | b | NON a | NON b | (NON a) ET (NON b) |

|---|---|---|---|---|

| x | y | x ET y | ||

| 0 | 0 | |||

| 0 | 1 | |||

| 1 | 0 | |||

| 1 | 1 |

Le OU exclusif logique entre deux booléens a et b se définit par :

| a | b | a XOR b |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

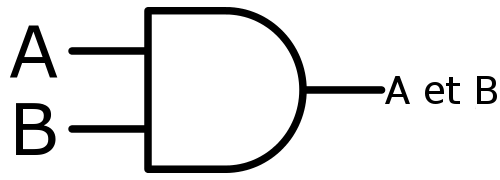

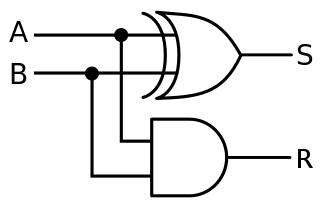

A chaque porte est associée une représentation graphique. Voici pour les portes ET et XOR :

Les opérations logiques évoquées ci-dessus sont mises en œuvre en électronique sous forme de portes logiques. Ainsi les circuits électroniques calculent des fonctions logiques de l'algèbre de Boole. Pour chacun des opérateurs logiques évoquées ci-dessus (et d'autres) il existe donc des portes logiques appelés porte ET, porte NON, etc. Les valeurs vrai et faux sont représentées par deux niveaux de tension, haut et bas. Un circuit de type porte ET dispose donc de deux entrées et une sortie et la valeur du niveau de tension en sortie dépend des niveaux de tension appliquées à chaque entrée, en respectant la table de vérité du ET. Les portes peuvent être connectées entre elles pour réaliser des circuits logiques et on peut ainsi réaliser des calculs.

Prenons l'exemple de ce circuit :

Il est appelé demi-additionneur car il réalise l'addition de 2 bits (A et B), le résultats de cette somme est représentée par S et la retenue éventuelle par R.

Pour plus d'info, aller sur wikipédia.

On va additionner 5 et 7, mais en binaire.

On vient de constater que pour additionner deux nombres binaires, il faut à chaque étape additionner 3 bits : le bit du premier nombre, le bit du deuxième nombre et le bit de la retenue.

| a | b | c | a+b+c |

|---|---|---|---|

| 0 | 0 | 0 | |

| 0 | 0 | 1 | |

| 0 | 1 | 0 | |

| 1 | 0 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 | |

| 1 | 1 | 1 |

Ces deux tableaux peuvent être interprétés comme des tables de vérité en remplaçant les 1 par VRAI et les 0 par FAUX.

En supposant que a et b sont des nombres binaires de 10 chiffres.

On va stocker les bits du premier nombre sous forme de VRAI/FAUX dans la liste n, de même pour le deuxième nombre dans la liste p et du résultat dans la liste r.

On peut en déduire l'algorithme suivant:

c=FAUX

POUR i allant de 0 à 9

a=n[i]

b=p[i]

r[i]=(a ET NON b ET NON c) OU (NON a ET b ET NON c) OU (NON a ET NON b ET c) OU ( a ET b ET c)

c=(a ET b) OU (b ET c) OU (a ET c)

FinPOUR

r[10]=c

Afficher r et écris le programmme de l'addition de 2 nombres binaires.

et écris le programmme de l'addition de 2 nombres binaires.Va dans l' , cours ISN et choisis Travaux : TP : Addition et dépose ton fichier .py avec ton code.

, cours ISN et choisis Travaux : TP : Addition et dépose ton fichier .py avec ton code.